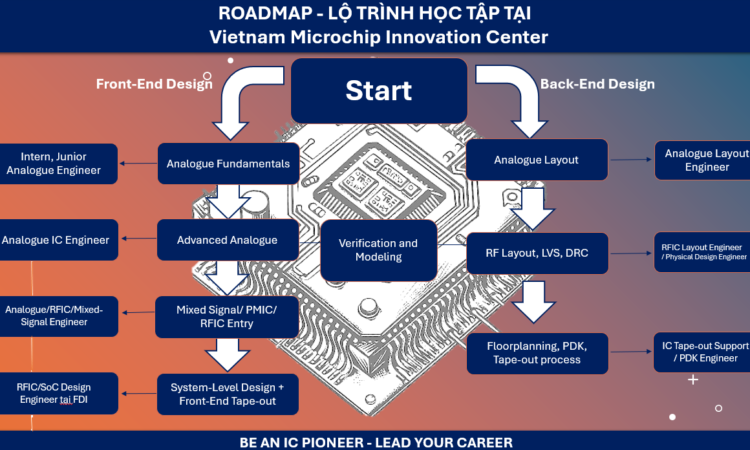

Thiết kế vi mạch tích hợp (IC Design) là một hành trình phức tạp, đòi hỏi sự phối hợp chặt chẽ giữa kiến trúc, logic và vật lý. Thiết kế vi mạch tích hợp biến một ý tưởng về chức năng thành hàng tỷ transistor được sắp xếp chính xác trên một miếng silicon nhỏ bé. Quá trình này được chia thành hai phần chính: Front-End (Thiết kế Logic) và Back-End (Thiết kế Vật lý), được thực hiện bằng các công cụ Tự động hóa Thiết kế Điện tử (EDA – Electronic Design Automation) chuyên dụng.

Mục lục

- 1. I. Giai đoạn Khởi tạo Thiết kế vi mạch: Xác định và Thiết kế Kiến trúc

- 2. II. Giai đoạn Front-End Design: Thiết kế và Xác minh Logic

- 3. III. Giai đoạn Back-End Design: Thiết kế Vật lý và Timing

- 4. III. Giai đoạn cuối trong quy trình thiết kế vi mạch/Giai đoạn Back-End Design: Thiết kế Vật lý và Timing

I. Giai đoạn Khởi tạo Thiết kế vi mạch: Xác định và Thiết kế Kiến trúc

-

Bản mô tả Kỹ thuật (Specification)

Đây là bước khởi đầu, nơi nhóm thiết kế xác định mục tiêu của chip. Bản Specification phải trả lời các câu hỏi quan trọng về PPA (Power, Performance, Area):

- Performance (Hiệu năng): Tần số hoạt động tối đa (ví dụ: ), độ trễ (latency), và băng thông.

- Power (Công suất): Công suất tiêu thụ tối đa (cả tĩnh và động) và yêu cầu quản lý nhiệt.

- Area (Diện tích): Kích thước chip (die size) và số lượng cổng logic cần thiết.

-

Thiết kế Kiến trúc (Architectural Design)

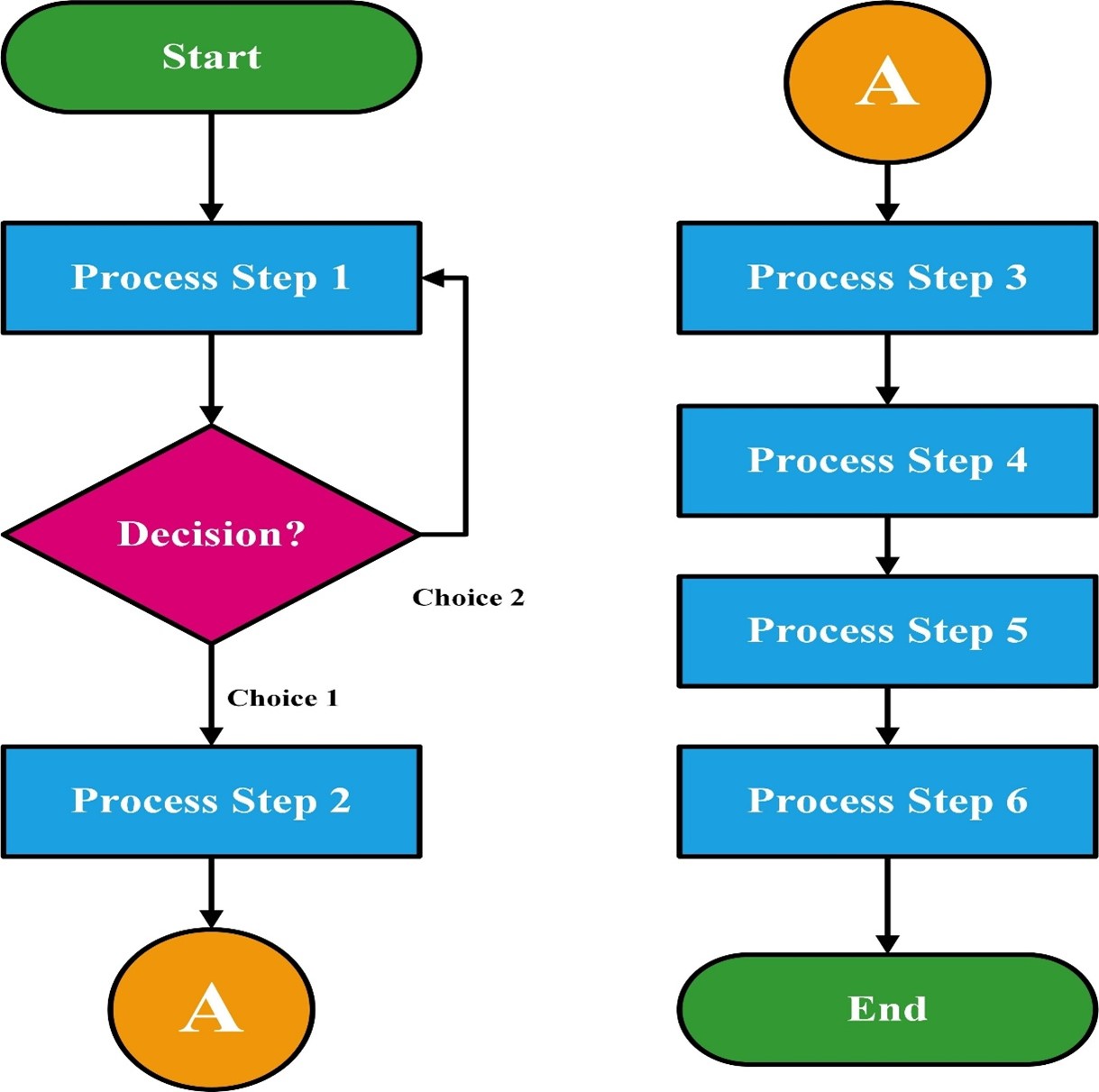

Sau khi có Specification, kiến trúc sư chia hệ thống phức tạp thành các khối chức năng nhỏ hơn (modules hoặc blocks). Bước này bao gồm việc xác định các giao thức giao tiếp (interfaces), phân bổ bộ nhớ, và lựa chọn kiến trúc xử lý (ví dụ: RISC-V, ARM). Quá trình này thường sử dụng mô hình cấp hệ thống (System-Level Modeling) bằng C++ hoặc SystemVerilog để đánh giá hiệu suất sơ bộ.

II. Giai đoạn Front-End Design: Thiết kế và Xác minh Logic

Giai đoạn Front-End trong quy trình thiết kế vi mạch tập trung vào việc mô tả hành vi chức năng (logic) của chip mà không bận tâm đến bố cục vật lý.

-

Mã hóa RTL (Register Transfer Level Coding)

Đây là giai đoạn viết mã logic của chip sử dụng các ngôn ngữ mô tả phần cứng (HDL – Hardware Description Language) như Verilog hoặc VHDL. RTL mô tả cách dữ liệu được truyền giữa các thanh ghi (Registers) và cách dữ liệu được xử lý bởi các mạch tổ hợp (Combinational Logic) trong mỗi chu kỳ xung nhịp (Clock Cycle).

-

Mô phỏng và Xác minh Chức năng (Functional Verification)

Verification (Xác minh) là bước quan trọng nhất, thường chiếm tổng thời gian thiết kế. Mục tiêu là đảm bảo mã RTL hoạt động chính xác theo Specification.

- Mô phỏng (Simulation): Chạy mã RTL với các tập dữ liệu đầu vào (testbenches) để kiểm tra tất cả các trường hợp sử dụng, bao gồm cả các trường hợp góc (corner cases).

- Xác minh Formal (Formal Verification): Sử dụng các công cụ toán học để chứng minh logic của chip là đúng, độc lập với các test vectors cụ thể.

- UVM (Universal Verification Methodology): Một phương pháp luận phổ biến để xây dựng các môi trường kiểm thử (test environments) có khả năng tái sử dụng cao.

-

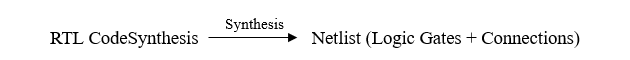

Tổng hợp (Synthesis)

Công đoạn này là cầu nối giữa logic và vật lý. Công cụ Synthesis sẽ dịch mã RTL (mô tả hành vi) thành một Netlist (danh sách kết nối) bao gồm các cổng logic cơ bản (Standard Cells) có sẵn trong thư viện của nhà sản xuất chip (Foundry).

Kết quả của Synthesis là một mạch chức năng được tạo thành từ các cổng AND, OR, NOT, Flip-Flops… đã được định hình kích thước vật lý.

III. Giai đoạn Back-End Design: Thiết kế Vật lý và Timing

Giai đoạn Back-End biến Netlist logic thành bố cục vật lý trên silicon, nơi các vấn đề về vật lý như thời gian, nhiễu và tiêu thụ năng lượng được giải quyết.

-

Phân tích Thời gian Tĩnh (Static Timing Analysis – STA)

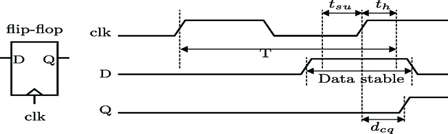

STA là công đoạn quan trọng nhất của Back-End, đảm bảo chip có thể hoạt động ở tần số mục tiêu. STA tính toán độ trễ (delay) của tín hiệu qua mọi đường dẫn trong chip để kiểm tra các vi phạm Setup Time và Hold Time của các Flip-Flops.

- Setup Time: Tín hiệu cần ổn định trước cạnh xung nhịp.

- Hold Time: Tín hiệu cần ổn định sau cạnh xung nhịp.

- Công cụ STA phải xem xét các điều kiện khắc nghiệt nhất (Worst-Case Scenarios) về điện áp và nhiệt độ.

Hiểu rõ mối quan hệ giữa Setup và Hold Time là chìa khóa để đảm bảo sự ổn định của hệ thống tuần tự, tránh tình trạng Meta-stability.

-

Lập kế hoạch Sàn và Bố trí (Floorplanning & Placement)

- Floorplanning: Xác định vị trí và kích thước tương đối của các khối chức năng lớn (ví dụ: bộ nhớ RAM, PLL, core logic) và vị trí của các chân I/O.

- Placement (Bố trí): Đặt hàng triệu cổng logic (Standard Cells) vào vị trí vật lý tối ưu trong khu vực đã được định nghĩa. Mục tiêu là giảm thiểu chiều dài dây dẫn để tối ưu hóa hiệu suất và giảm công suất.

-

Định tuyến Dây dẫn và Cấu trúc Đồng hồ (Routing & CTS)

- Clock Tree Synthesis (CTS): Tạo ra một mạng lưới dây dẫn đồng hồ cân bằng, đảm bảo xung nhịp đến tất cả các Flip-Flop cùng một lúc (giảm thiểu Clock Skew), đây là yếu tố then chốt cho STA.

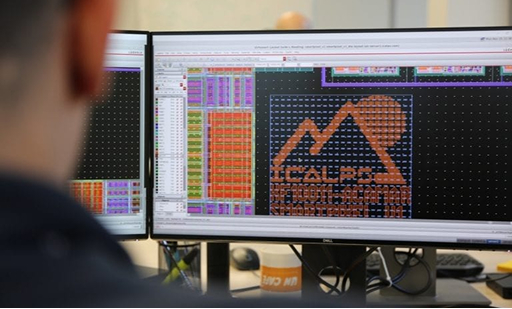

- Routing (Định tuyến): Nối dây các cổng logic theo Netlist. Quá trình này sử dụng nhiều lớp kim loại (Metal Layers) chồng lên nhau và phải tuân thủ nghiêm ngặt các quy tắc thiết kế (DRC – Design Rule Check) của Foundry.

- Kiểm tra Vật lý Cuối cùng (Physical Verification)

Trước khi gửi đi sản xuất (Tape-out), Netlist vật lý phải được kiểm tra kỹ lưỡng:

- DRC (Design Rule Check): Kiểm tra các lỗi vật lý cơ bản (ví dụ: khoảng cách tối thiểu giữa hai dây dẫn, kích thước lỗ VIA).

- LVS (Layout Versus Schematic): So sánh bố cục vật lý (Layout) với Netlist logic ban đầu (Schematic) để đảm bảo không có lỗi kết nối nào xảy ra trong quá trình P&R.

- ERC (Electrical Rule Check): Kiểm tra tính toàn vẹn tín hiệu (Signal Integrity) và tính toàn vẹn nguồn (Power Integrity) như IR Drop (sụt áp nguồn) và Crosstalk (nhiễu xuyên âm).

Kiểm tra DRC/LVS là bước cuối cùng để đảm bảo bố cục vật lý có thể sản xuất được và khớp hoàn toàn với sơ đồ logic ban đầu.

III. Giai đoạn cuối trong quy trình thiết kế vi mạch/Giai đoạn Back-End Design: Thiết kế Vật lý và Timing

Tape-out và Chế tạo (Fabrication)

Dữ liệu bố cục cuối cùng (GDSII file) được gửi đến nhà máy đúc (Foundry). Foundry sử dụng các tệp này để tạo ra các mặt nạ quang học (Photomasks) và tiến hành quá trình khắc quang (Lithography) phức tạp trên các Silicon Wafer.

Đóng gói và Thử nghiệm (Packaging & Testing)

- Các chip trên Wafer được cắt (dicing) và gắn vào lớp vỏ bảo vệ (Package).

- Các kỹ sư chạy các bài kiểm tra chức năng và thông số kỹ thuật (Specification Tests) cuối cùng để loại bỏ các chip lỗi (Testing/Yield Analysis), đảm bảo chỉ các sản phẩm đạt chất lượng mới được đưa ra thị trường.

Quy trình thiết kế vi mạch là một chuỗi các bước kiểm soát nghiêm ngặt, từ trừu tượng (RTL) đến cụ thể (Layout), nhằm đảm bảo chip không chỉ hoạt động đúng logic mà còn tuân thủ tuyệt đối các ràng buộc vật lý về PPA.