Trung tâm Đổi mới Vi mạch Việt Nam VMIC Edu gửi đến bạn quá trình phân tích, tính toán và mô phỏng mạch khuếch đại thuật toán CMOS (Operational Amplifier Op-Amp), sử dụng cấu hình phản hồi điện áp (series–shunt feedback). Nghiên cứu tập trung xác định các điểm làm việc tĩnh, tham số tín hiệu nhỏ, hệ số khuếch đại vòng lặp và phản hồi, cũng như độ lợi vòng kín của mạch.

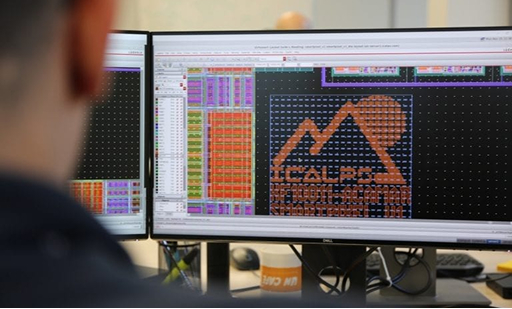

Các kết quả mô phỏng được thực hiện bằng phần mềm LTspice, cho phép so sánh giữa mô hình lý thuyết và thực nghiệm mô phỏng.

Kết quả cho thấy sự sai lệch nhỏ giữa hai mô hình chủ yếu đến từ ảnh hưởng của tham số điều biến chiều dài kênh (λ).

Qua đó, bài viết giúp người học hiểu rõ cơ chế hoạt động của Op-Amp CMOS và vai trò quan trọng của phản hồi trong việc cải thiện tuyến tính và ổn định mạch.

Mục lục

- 1. Khuếch đại thuật toán là gì?

- 2. Cơ sở lý thuyết của mạch khuếch đại thuật toán

- 3. Tính toán và mô phỏng mạch Op-Amp CMOS như thế nào?

- 3.1. Tính tham số tín hiệu nhỏ gm và rds cho từng transitor trong Op-Amp CMOS

- 3.2. Đánh giá sự ảnh hưởng của λ, tính toán lại các điện áp phân cực cần thiết, mô phỏng bằng LTspice

- 3.3. Phân tích độ lợi vòng lặp và hệ số phản hồi của mạch khuếch đại CMOS

- 3.4. Hệ số phản hồi và độ lợi vòng hở

- 3.5. Độ lợi vòng kín và điện trở đầu ra vòng kín

- 4. Kết luận về việc phân tích, tính toán và mô phỏng mạch khuếch đại thuật toán CMOS sử dụng cấu hình phản hồi điện áp

Khuếch đại thuật toán là gì?

Khuếch đại thuật toán (Operational Amplifier – Op-Amp) là khối mạch cơ bản trong các hệ thống xử lý tín hiệu tương tự. Với công nghệ CMOS, các Op-Amp hiện đại có ưu điểm tiêu thụ công suất thấp, độ tích hợp cao và khả năng hoạt động ổn định trên nhiều điều kiện tải khác nhau. Tài liệu dưới đây sẽ hướng dẫn người học phân tích và thiết kế một mạch Op-Amp CMOS theo cấu hình phản hồi điện áp. Mục tiêu chính là xác định điện áp bias, dòng làm việc tĩnh, tham số tín hiệu nhỏ, hệ số khuếch đại vòng lặp, phản hồi và khuếch đại vòng kín.

Cơ sở lý thuyết của mạch khuếch đại thuật toán

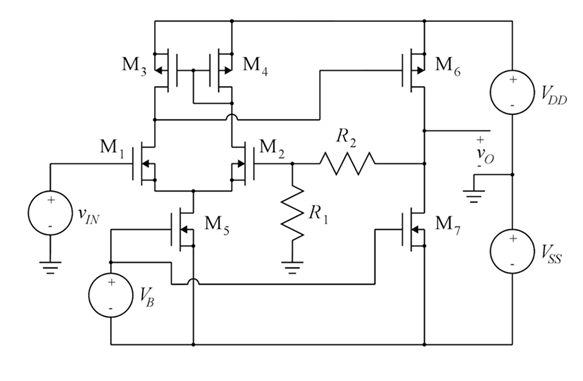

Dưới đây là một sơ đồ mạch ví dụ của một mạch Op-Amp CMOS

Mạch Op-Amp CMOS bao gồm các tầng chính sau:

- Tầng vi sai đầu vào: gồm hai transistor NMOS M1 và M2, khuếch đại sai lệch điện áp đầu vào.

- Tầng tải chủ động: hai PMOS M3 và M4 hoạt động như tải gương dòng.

- Tầng khuếch đại điện áp: transistor PMOS M5 đảm nhận khuếch đại chính, kết hợp với NMOS M6 tạo tầng khuếch đại điện áp.

- Tầng đầu ra: transistor M7 cung cấp khả năng khuếch đại dòng ra và ổn định điện áp tải.

Cấu hình phản hồi điện áp (series–shunt feedback) được áp dụng để lấy mẫu điện áp ngõ ra và đưa ngược trở lại đầu vào.

Phản hồi âm giúp ổn định độ lợi, giảm méo và cải thiện dải tần hoạt động.

Trong trạng thái cân bằng, điện áp sai lệch giữa hai đầu vào gần bằng 0, bảo đảm tuyến tính cao.

Tính toán và mô phỏng mạch Op-Amp CMOS như thế nào?

Thông số ban đầu

Tất cả transistor trừ M5 có µCox(W/L) = 0.1 mA/V², riêng M5 có µCox (W/L) = 0.2 mA/V².

Các thông số khác:

– Ngưỡng điện áp NMOS: Vth = 0.6 V

– Ngưỡng điện áp PMOS: Vth = –0.6 V

– Hệ số điều biến chiều dài kênh: λ = 0.05 V⁻¹

– Điện áp đầu vào VIN =0V

– Nguồn cấp: VDD = VSS = 5 V

– Điện trở: R1 = 2 kΩ, R2 = 10 kΩ

Mục tiêu: Dòng qua M5 cần đạt ID5 = 360 µA.

Mô hình Shichman–Hodges

Phương trình cơ bản cho transistor hoạt động trong vùng bão hòa:

Xác định các điện áp bias của các transitor và xác định giá trị tĩnh của điện áp transitor, bỏ qua λ:

Ta có:

Với M5

Các transistor M1–M4 vì lí do đối xứng, có ID = ID5 /2 = 180 µA,

Transitor M7 có ID = ID5 /2 = 180 µA vì lý do tỉ lệ giữa M5 và M7

Transitor M6 có ID6 = ID7 = 180 µA

Vì tất cả các transistor đều có cùng mật độ dòng điện và hoạt động ở vùng bão hòa, chúng đều có điện áp gate-source là 2.5V, với transitor NMOS, VGS là dương. Với transistor CMOS, VGS là âm

Toàn bộ transistor hoạt động trong vùng bão hòa.

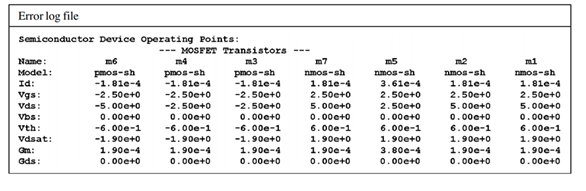

Tính tham số tín hiệu nhỏ gm và rds cho từng transitor trong Op-Amp CMOS

Sử dụng các giá trị xấp xỉ của dòng điện và điện áp đã tính toán ở phần trước, ta có

Tính toán: gm5 = 2 x 360 µA/(2.5 V-0.6 V) = 0.38 mA/V

Với các giá trị transistors khác, gm=0.19 mA/V

Với điện trở đầu ra rds tính bằng công thức:

Với M1 và M2, ta có rds = (1 + 0.05 V-1 x 5V)/(0.05 V-1 x 180 µA) = 139 kΩ

Tương tự ta có với M3 và M4, rds = 125 kΩ

Với M5, rds = 62.5 kΩ

Với M6 và M7, rds = 139 kΩ

Đánh giá sự ảnh hưởng của λ, tính toán lại các điện áp phân cực cần thiết, mô phỏng bằng LTspice

Với

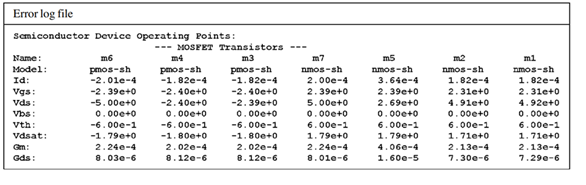

Sai số giữa tính toán và mô phỏng nhỏ, do λ làm tăng nhẹ dòng qua transistor.

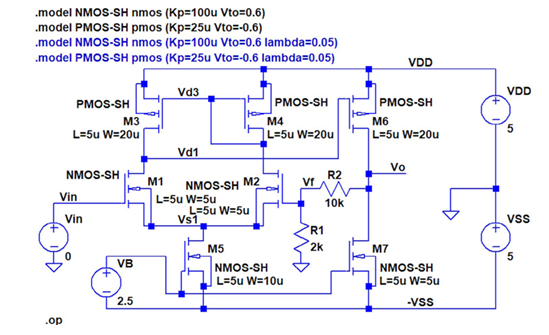

Mô phỏng LTspice

Mạch được mô phỏng với các thông số như trên.

Kết quả mô phỏng khi λ=0

Kết quả mô phỏng khi λ = 0.05 V-1

Kết quả cho thấy các giá trị ID, VGS, VDS và gm khớp tốt với lý thuyết khi λ = 0.

Khi λ = 0.05 V⁻¹, dòng qua M6 và M7 tăng nhẹ, VGS giảm một chút, dẫn đến gm tăng và rds giảm.

Phân tích độ lợi vòng lặp và hệ số phản hồi của mạch khuếch đại CMOS

Phần này tập trung tính toán độ lợi vòng lặp (loop gain) và hệ số phản hồi (feedback factor) của mạch khuếch đại thuật toán CMOS có phản hồi điện áp. Mục tiêu là đánh giá mối quan hệ giữa độ lợi vòng hở, phản hồi và độ lợi vòng kín thông qua mô hình tín hiệu nhỏ của các tầng vi sai và khuếch đại chung nguồn

Độ lợi vòng lặp được xác định theo biểu thức:

Thay giá trị đã tính:

= 12.5 x 1.96 x 0.167 V/V = 4.08V

Khi đưa hiệu ứng điều biến chiều dài kênh (λ = 0,05 V⁻¹) vào mô phỏng, kết quả cho

= 13.81 × 2.25 × 0.167 V/V = 5.19 V/V

Mô phỏng trên LT spice

Hệ số phản hồi và độ lợi vòng hở

Hệ số phản hồi được xác định bởi bộ chia điện áp:

Kết quả chứng tỏ mô hình tính toán phù hợp tốt với mô phỏng. Độ lợi vòng lặp khoảng 4–5 V/V và hệ số phản hồi 0,167 V/V cho độ lợi vòng hở ~25-30 V/V. Phản hồi điện áp làm giảm độ lợi tổng nhưng cải thiện tuyến tính và ổn định mạch.

Độ lợi vòng kín và điện trở đầu ra vòng kín

Sử dụng các giá trị đã tính cho (độ lợi vòng hở) và (loop gain), ta tính được độ lợi vòng kín theo công thức tiêu chuẩn:

Thay các giá trị đã tính vào:

Với các giá trị tính toán (theo phân tích nhỏ): Α = 24.4 và β = 0.167 nên

Với các giá trị mô phỏng (giá trị A và L lấy từ kết quả LTspice), ta tìm được:

ACL,sim = 5.02 V/V

Kết quả đo trực tiếp từ file xuất ra LTspice (dùng lệnh .tf v(Vo) Vin) cho giá trị

ACL,tf = 5.03 V/V

Điện trở đầu ra vòng kín được giảm bởi hệ số 1+βΑ . Nếu Rout là điện trở đầu ra của mạch A (mạch không có mạng phản hồi), thì giá trị tính toán

Giá trị mô phỏng

Giá trị lấy trực tiếp từ kết quả mô phỏng LTspice (từ .tf hoặc phương pháp đo xiết mạch) là

![]()

Độ lợi vòng kín tính toán 4.82 V/V và kết quả mô phỏng 5.02-5.03 V/V khớp tốt (chênh lệch nhỏ, do làm tròn tham số và ảnh hưởng của λ, các điện áp VDS thực tế). Điện trở đầu ra vòng kín giảm mạnh so với điện trở đầu ra mạch A nhờ hệ số 1+βΑ ; mô phỏng cho giá trị khoảng 1.66 kΩ. Sự khác biệt nhỏ giữa “tính toán” và “mô phỏng” đến từ: làm tròn các tham số nhỏ-signal trong bảng, ảnh hưởng của channel-length modulation (λ) và các điều kiện điểm làm việc thực tế trong LTspice.

Kết luận về việc phân tích, tính toán và mô phỏng mạch khuếch đại thuật toán CMOS sử dụng cấu hình phản hồi điện áp

Bài viết đã trình bày quá trình phân tích và mô phỏng một mạch khuếch đại thuật toán CMOS có phản hồi điện áp. Thông qua việc xác định điểm làm việc tĩnh, tính toán tham số tín hiệu nhỏ, và mô phỏng LTspice, kết quả cho thấy mạch hoạt động ổn định, các giá trị mô phỏng khớp với tính toán lý thuyết. Phản hồi âm giúp giảm độ lợi vòng hở nhưng tăng tuyến tính và ổn định mạch. Phương pháp tiếp cận trong bài có thể áp dụng cho các cấu trúc Op-Amp CMOS khác nhau, đồng thời cung cấp nền tảng cho việc nghiên cứu thiết kế mạch khuếch đại công suất thấp và tốc độ cao trong các hệ thống tích hợp hiện đại.

TÀI LIỆU THAM KHẢO

[1] CMOS Analog IC Design – Learning by Problem Solving, Bookboon.

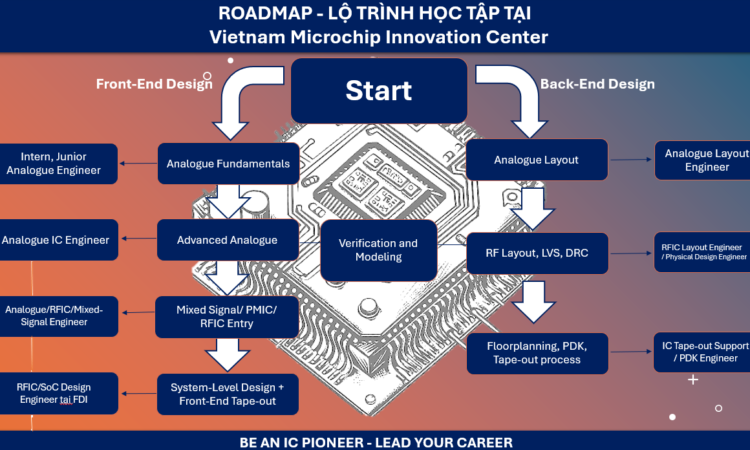

Trung tâm Đổi mới Vi mạch Việt Nam (Vietnam Microchip Innovation Center) mong muốn mang đến đội ngũ kỹ sư trẻ của Việt Nam nguồn kiến thức chuyên sâu, kinh nghiệm thực tiễn, và tư duy hiện đại để phát triển và giải quyết được các bài toán thiết kế chip trong thời đại mới.